Simularea

circuitelor cu porţi logice CMOS

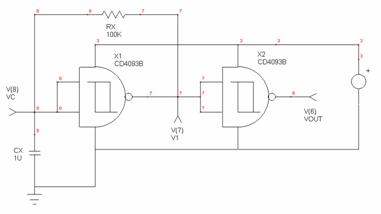

1. Se

dă circuitul din figura de mai jos:

Se cer:

a) Să se

simuleze funcţionarea circuitului (.TRAN) - se consideră Vcc = 12V;

b) Să se

explice formele de undă obţinute (Vc

şi Vout);

c) Se va

modifica valoarea lui Cx la 1uF, 10uF şi 100uF

şi se vor nota într-un tabel valoarea lui Cx

şi frecvenţa de oscilaţie;

d) Se va observa

modificarea frecvenţei de oscilaţie o dată cu modificarea

tensiunii de alimentare. Să se explice acest fenomen;

e) Se va nota

în caietul de laborator conţinutul fişierul cu extensia *.CIR aferent

circuitului simulat şi se va examina circuitul cu extensia *.OUT

explicându-se conţinutul fiecărei secţiuni în parte.

f) Să se explice dependenţa dintre valoarea

tensiunii de alimentare şi frecvenţa de oscilaţie a circuitului.

Observaţie: se vor nota în caietul de laborator

toate formele de undă (Vc şi Vout) obţinute la simulări (împreună cu

valorile numerice). Se vor nota şi comenzile de control a simulării

(din meniul File -> Edit Controls)

în cazul fiecărei simulări.

2. Să se simuleze circuitul fără poarta X2 iar la ieşirea

porţii X1 să se conecteze o rezistenţă de sarcină de 100k,

10k şi mai apoi de 0.1k. Să se explice de ce se modifică

frecvenţa de oscilaţie iar pentru valori foarte mici ale

rezistenţei de sarcină circuitul nu mai oscilează deloc.